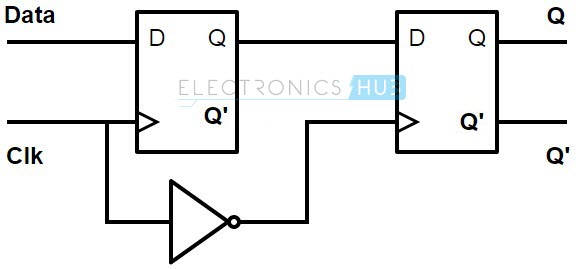

Hence, whatever value was at D immediately before the clock rises from 0 to 1 gets copied to Q immediately after the clock rises.

The value at N1 propagates through to Q, but N1 is cut off from D. When CLK = 1, the master goes opaque and the slave becomes transparent. Therefore, whatever value was at D propagates through to N1. When CLK = 0, the master latch is transparent and the slave is opaque. The term flip-flop or latch by itself usually refers to a D flip-flop or D latch, respectively, because these are the types most commonly used in practice. Bistable elements without an edge-triggered clock are commonly called latches. The state of the flip-flop changes only in response to a clock edge, such as when the clock rises from 0 to 1. In other words, it is a bistable element with a clock input. In common industry usage, a flip-flop is edge-triggered. The precise distinction between flip-flops and latches is somewhat muddled and has evolved over time. Later standards, DDR2, DDR3, and DDR4, increased the clock speeds, with speeds in 2021 being over 3 GHz. DDR was first standardized in 2000 and ran at 100 to 200 MHz. DDR SDRAM, sometimes called simply DDR, uses both the rising and falling edges of the clock to access data, thus doubling the throughput for a given clock speed. SDRAM uses a clock to pipeline memory accesses. DRAM technologies such as synchronous DRAM ( SDRAM) and double data rate ( DDR) SDRAM have been developed to overcome this problem. DRAM also fundamentally has lower throughput than SRAM, because it must refresh data periodically and after a read. DRAM must wait for charge to move (relatively) slowly from the capacitor to the bitline. DRAM latency is longer than that of SRAM because its bitline is not actively driven by a transistor. Generally, the more transistors a device has, the more area, power, and cost it requires. But flip-flops take at least 20 transistors to build. The data bit stored in a flip-flop is available immediately at its output. Table 5.6 shows a comparison of these three types of volatile memory.

Flip-flops, SRAMs, and DRAMs are all volatile memories, but each has different area and delay characteristics.

0 kommentar(er)

0 kommentar(er)